# Experimental Characterization of Monolithic Integrated Interleavers

Jessica César-Cuello<sup>1</sup>, Alberto Zarzuelo<sup>1</sup>, Robinson C. Guzmán<sup>2</sup>, and Guillermo Carpintero<sup>1</sup>

<sup>1</sup>Universidad Carlos III de Madrid, Av. Universidad 30, Leganés, 28911, Spain

<sup>2</sup>Universidad Rey Juan Carlos, Cam. del Molino 5, Fuenlabrada, 28942, Spain

1550

1550.45

#### Introduction

In this work, we present the experimental characterization of two monolithically integrated optical pulse interleavers implemented using asymmetric Mach-Zehnder interferometers (AMZIs). These devices are compact, robust, and highly scalable, making them ideal for integration into larger photonic systems. The interleavers use carefully designed optical delay lines to achieve frequency multiplication with delays of 20 GHz and 40 GHz, respectively.

Parameters such as extinction ratio (ER), resonant frequency tuning range, and free spectral range (FSR) highlight the performance of the devices. By incorporating phase modulators (PM), the interleavers demonstrate tunability beyond 15 GHz, providing flexibility to adapt to varying system requirements. This work aims to bridge the gap between theoretical designs and practical implementations, and to demonstrate the potential of monolithically integrated interleavers for next-generation high-speed optical systems.

### The Photonic Integrated Circuit

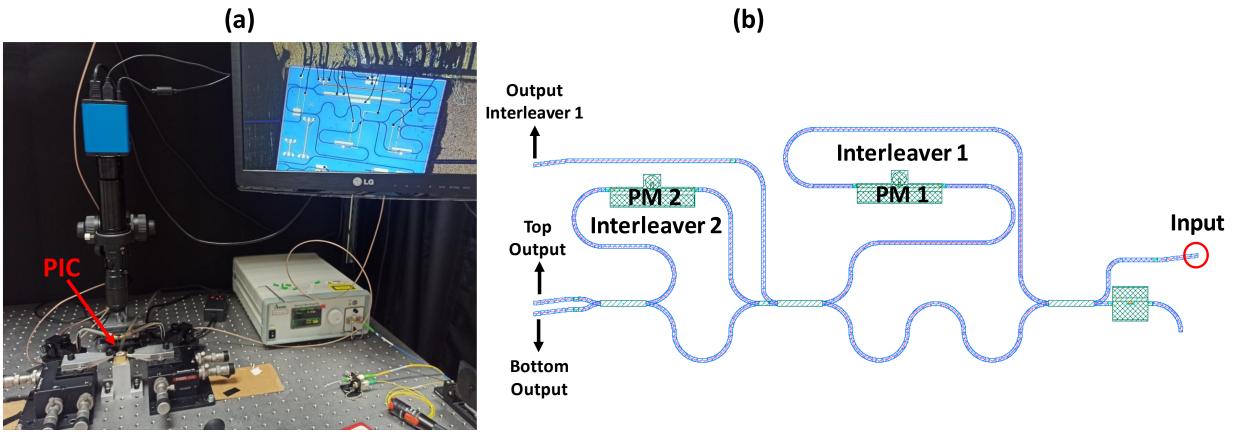

Fig. 1 presents a photograph and the corresponding layout of the devices under test. The PIC, measuring 4 mm × 4.6 mm, was fabricated through a multi-project wafer run provided by Smart Photonics. The device was developed using their monolithic InP active/passive integration platform, enabling integration of active and passive components within the same chip.

Fig. 1. (a) Photograph of the PIC showcasing the two interleaver structures. (b) Schematic layout of the system under test, illustrating the configuration and key components.

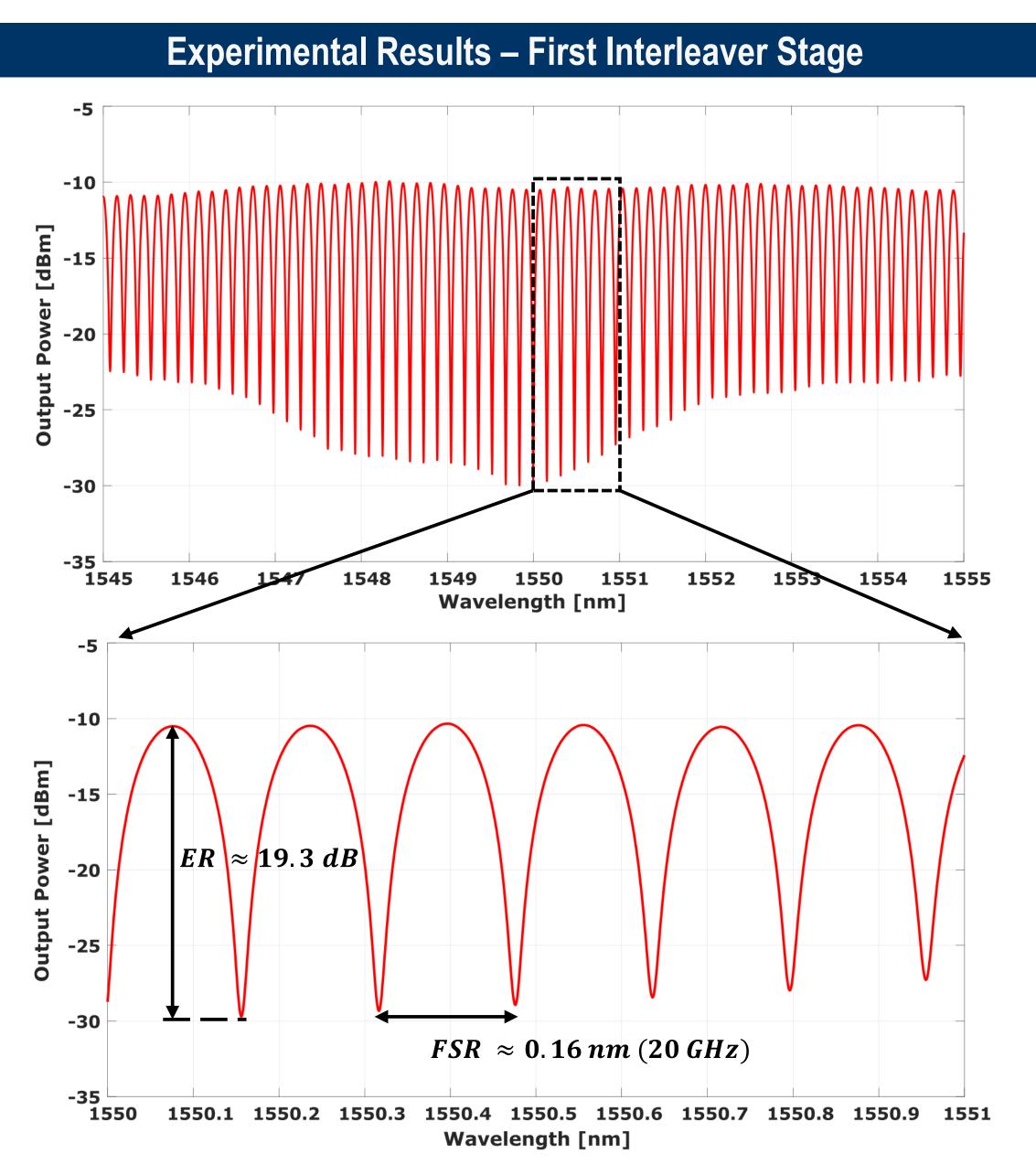

The first pulse interleaver stage was designed with an optical path length imbalance of 4.18 mm between its two arms, corresponding to an FSR of 20 GHz. Similarly, the second pulse interleaver stage features a reduced optical path length difference of 2.09 mm, enabling the doubling of the repetition rate to 40 GHz.

The structure exhibits an FSR of 20 GHz, meeting the desired design specifications. Additionally, it demonstrates a maximum ER of approximately 20 dB, indicating its strong ability to suppress unwanted signals outside the passband. The insertion loss was measured at each facet using a lensed fiber with a 2  $\mu$ m spot diameter, coupled to waveguides with a width of 1.5  $\mu$ m. These measurements revealed an insertion loss of around 4 dB.

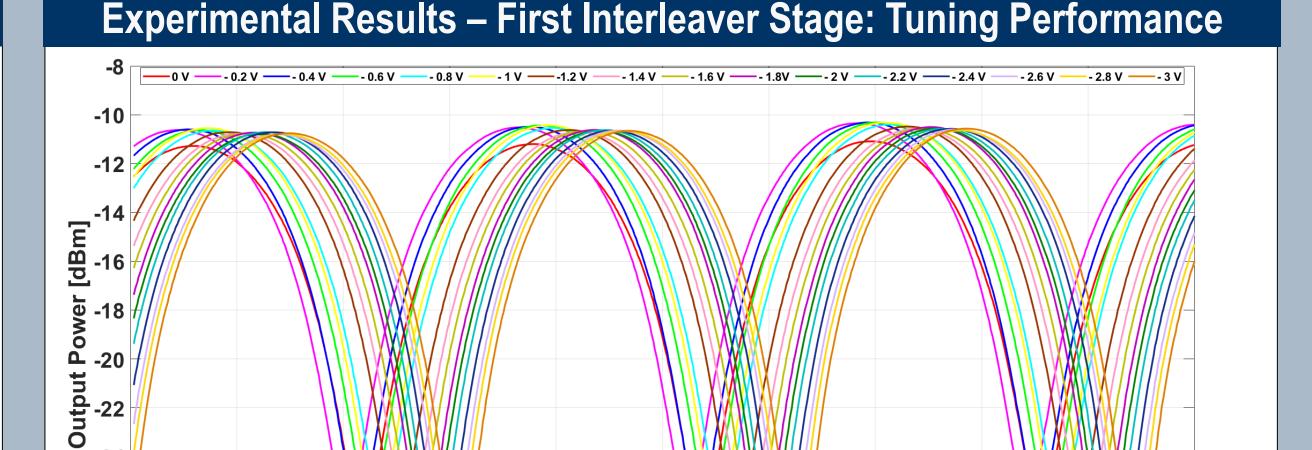

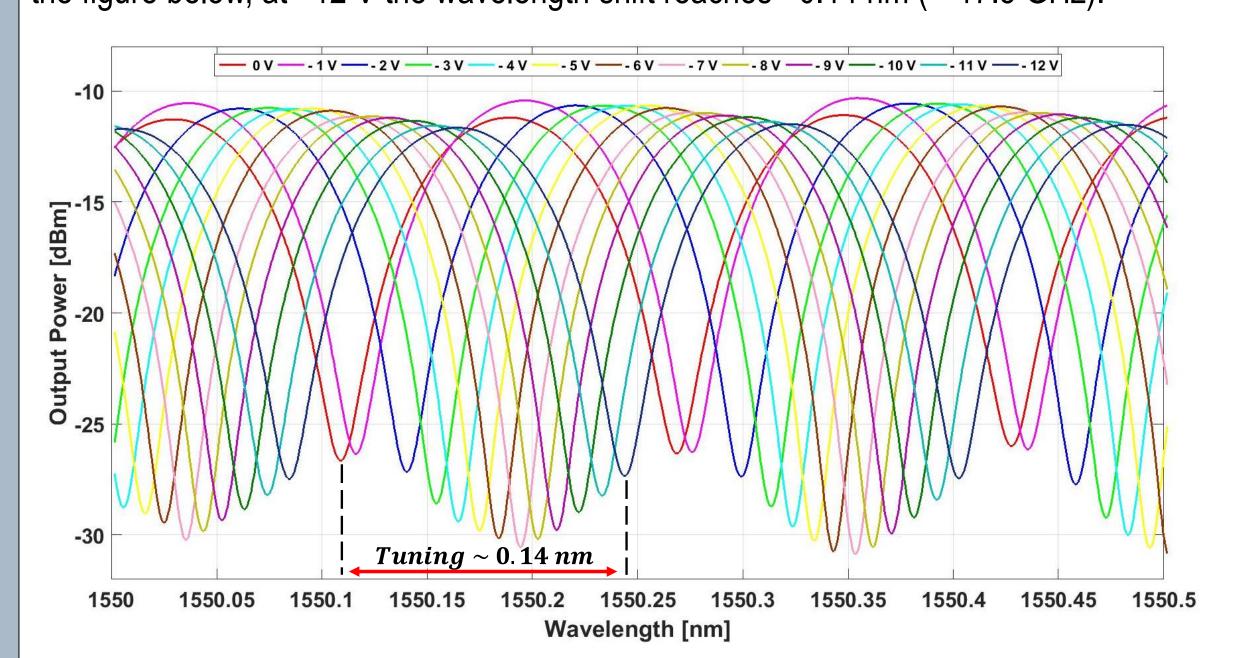

The phase modulator was reverse-biased from 0 V to -3 V in 0.2 V steps. As shown in the figure above, increasing the reverse bias to -3 V results in a wavelength shift of  $\sim$ 0.05 nm ( $\approx$  6.25 GHz), demonstrating precise control over the resonant frequency. Extending the reverse bias beyond -3 V further increases the tuning range. As shown in the figure below, at -12 V the wavelength shift reaches  $\sim$ 0.14 nm ( $\approx$  17.5 GHz).

Wavelength [nm]

1550.35

Tuning  $\sim 0.05 nm$

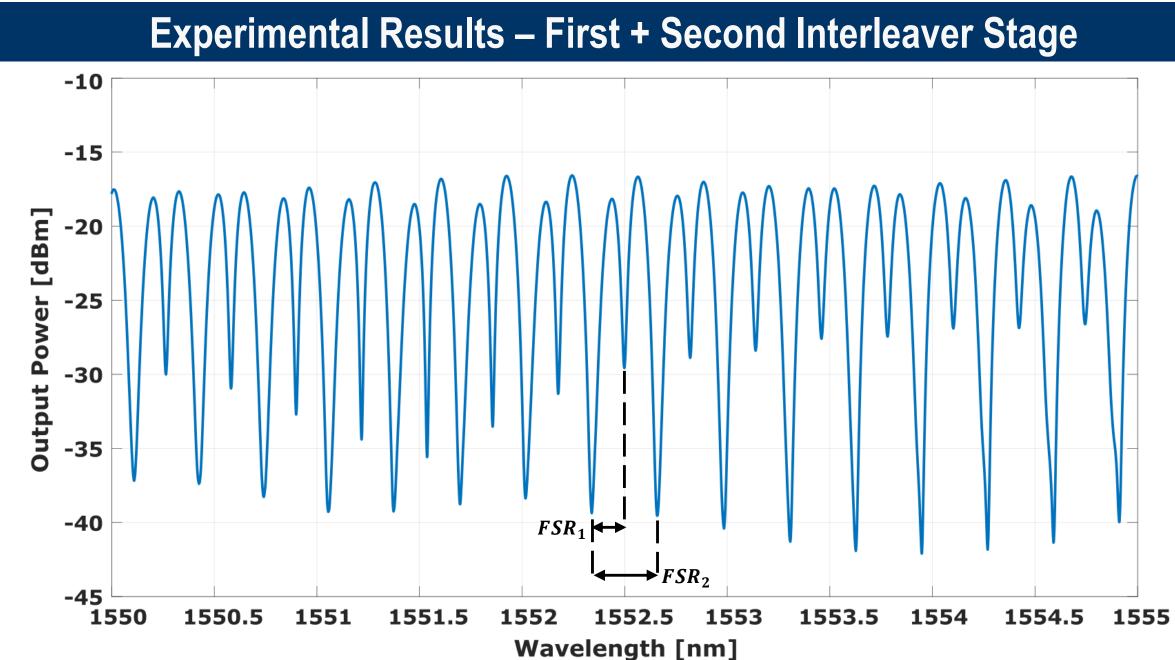

As shown in the figure, the output spectrum of the second structure clearly exhibits both expected FSRs of 20 GHz and 40 GHz. Additionally, the ER is well maintained across the spectrum, reaching a maximum value of 26 dB, indicating high filtering performance.

## Conclusions

We presented the experimental characterization of two sequential monolithic optical pulse interleaver structures. The monolithic integration of these interleavers on a single photonic chip offers key advantages, including compactness, robustness, and scalability. The structures demonstrated extinction ratios exceeding 20 dB and a resonance frequency tunability range greater than 15 GHz, highlighting their potential for dynamic spectral control.

## Acknowledgements

This work has been supported by the Unión Europea- NextGenerationEU and the Ministerio para la Transformación Digital y de la Función Pública through the Project "Tecnologías Avanzadas de Test, Ensamblaje y Encapsulado de Circuitos Integrados Electrónicos y Fotónicos - EPIC-Pack" (TSI-069100-2023-6); by the European Union through the project TERA6G (GA 101096949); and by the European Union through the project POLYNICES (G.A.101070549).

Chip